ARSENE

Défi : la sécurité matérielle et logicielle des systèmes embarqués

Aperçu

Développer de nouvelles technologies souveraines pour des systèmes embarqués intrinsèquement sécurisés.

Romain Wacquez, Responsable de programme CEA

David Hély, Professeur Grenoble-INP UGA

L’objectif du projet ARSENE est de contribuer aux travaux de recherche de la communauté française sur la sécurisation des processeurs, la sécurisation de leurs intégrations dans les ‘system on chip’, les nouvelles primitives de sécurité, des méthodologies et outils pour la sécurisation des logiciels embarqués et des noyaux sécurisés des systèmes d’exploitation. Ces nouvelles technologies seront mises en œuvre et démontrées au travers de composants ASIC dédiés.

Mots clefs : Sécurité des processeurs RISC-V, mémoires sécurisées, RNG, PUF, accélérateurs cryptographiques, outils de compilation, outils d’aide à la conception sécurisée, système d’exploitation embarqué, véhicules de tests.

Faire évoluer

Nos recherches

Sécurisation des implémentations de processeurs pour des composants IoT ou pour des applications plus riches

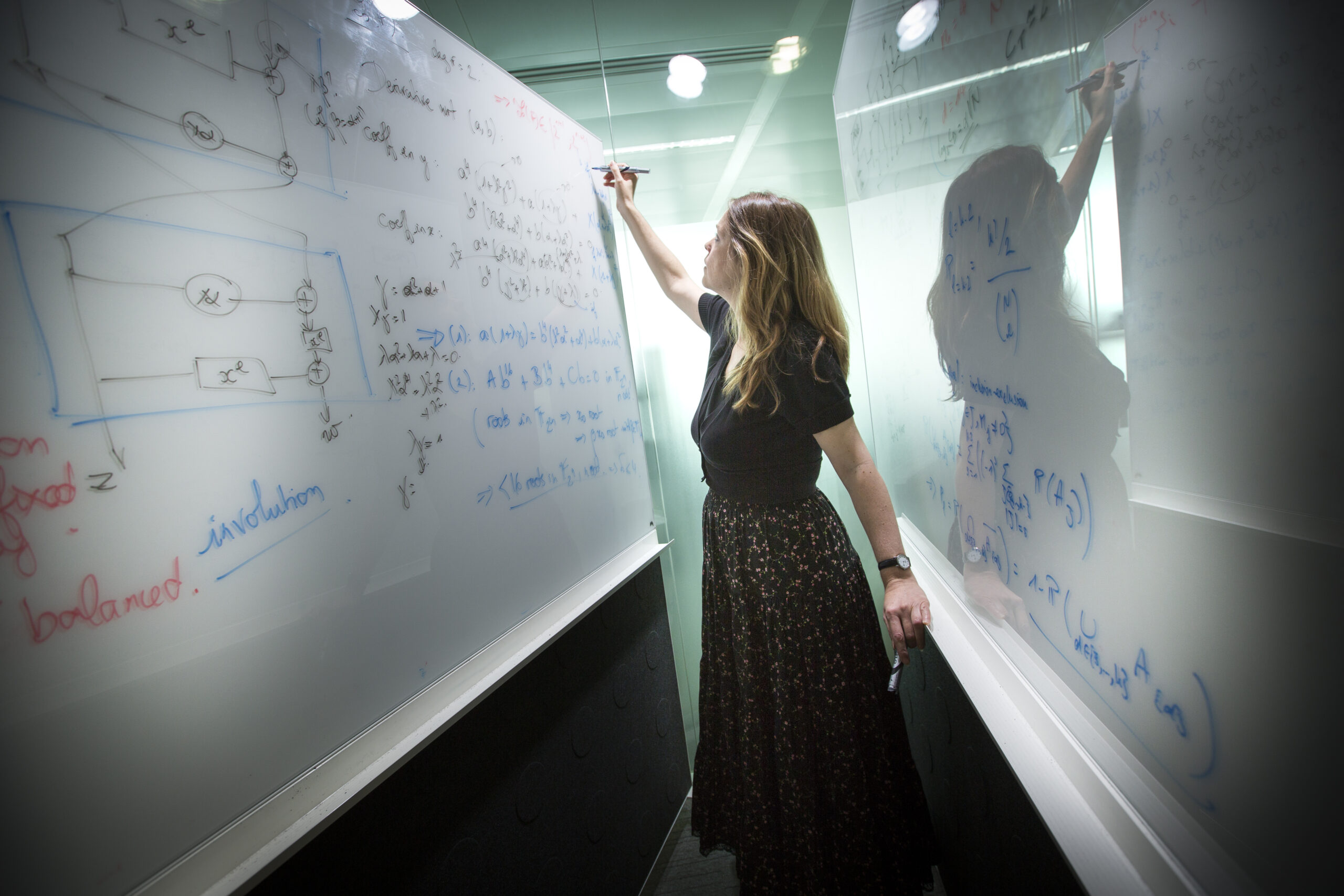

Une première partie des travaux menés au sein d’ARSENE porte sur la sécurisation des implémentations de références de deux gammes de processeurs RISC-V : RISC-V 32 bits, pour des applications IoT contraintes, intrinsèquement sécurisées contre les attaques physiques, et RISC-V 64 bits pour des applications plus riches, particulièrement sécurisées contre les attaques logicielles exploitant les failles matérielles.

Intégration sécurisée des processeurs au sein de systèmes sur puce embarquant des éléments mémoires ou cryptographiques sécurisés

L’intégration sécurisée de ces processeurs au sein de systèmes sur puce (SoC) hétérogène est un second aspect étudié dans ce projet, ainsi que la recherche et le développement de briques critiques pour de tels SoC, notamment des générateurs de nombres aléatoires robustes et fiables, des mémoires sécurisées contre les attaques physiques, des mémoires fonctionnalisées pour la sécurité et des accélérateurs cryptographiques agiles pour algorithmes dits « pré et post-quantiques ».

Les outils logiciels pour l’annotation dynamique de code et pour la génération de codes sécurisés

Ces travaux sur le matériel sont complétés par l’étude d’outils logiciels pour l’annotation dynamique de code et pour la génération de codes sécurisés, par l’étude et la mise en œuvre de noyaux sécurisés pour OS embarqués, et par la recherche sur des techniques de supervision dynamique d’exécution sécurisée.

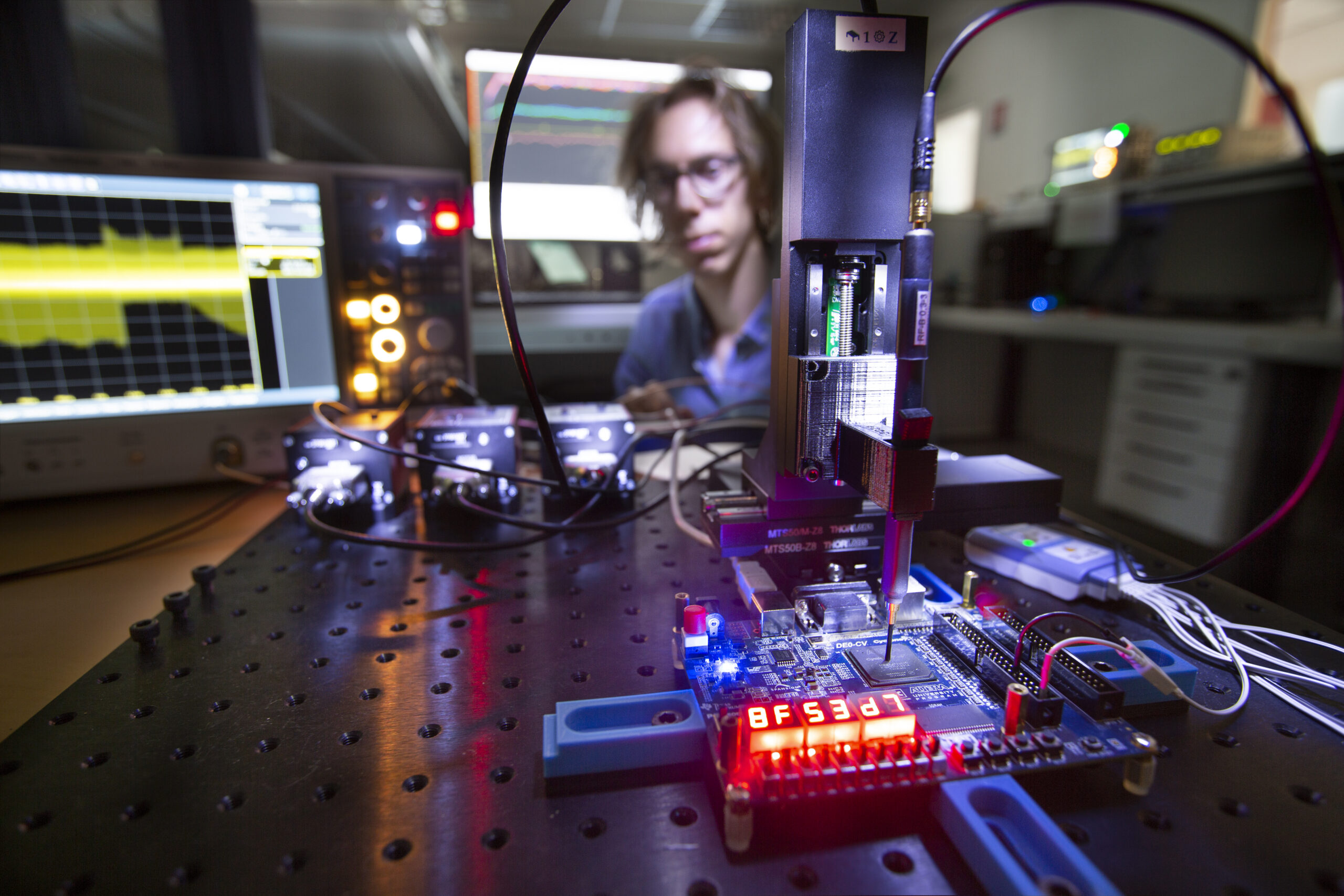

Ces travaux seront démontrés et validés à travers la mise en œuvre et le test de preuves de concept sur des composants de type FPGA et ASIC.

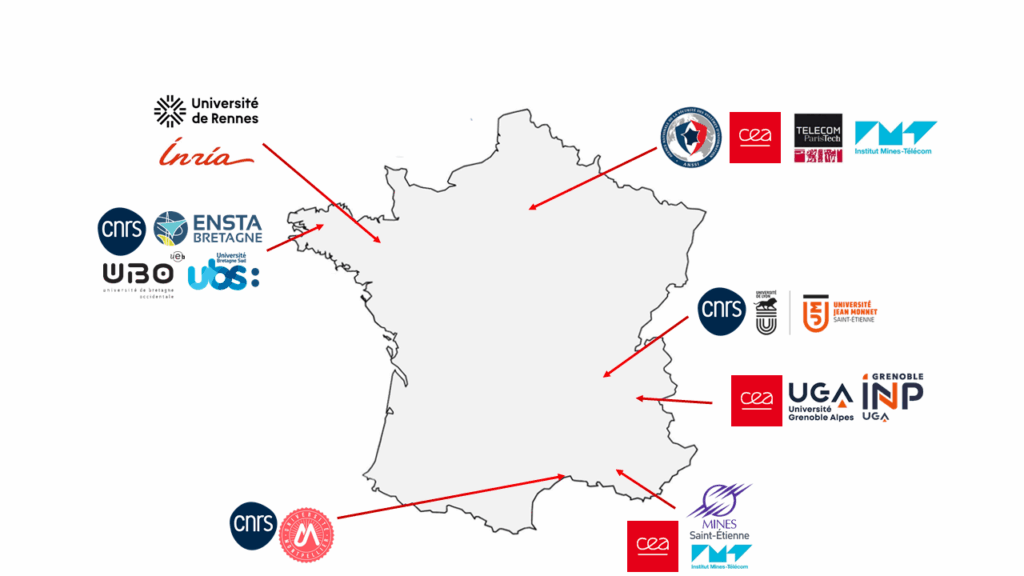

Le consortium

CEA, CNRS, Inria, IMT, Grenoble INP – UGA, ANSSI

Les principaux objectifs scientifiques sont d’améliorer les architectures sécurisées de processeurs, la sécurisation des mémoires embarquées, et le développement d’accélérateurs cryptographiques, les outils d’aide à la conception sécurisée.

La particularité du projet porte aussi sur l’ambition d’avoir des prototypes et démonstrateurs FPGA et ASIC

Ce projet permet d’améliorer, à travers de technologies souveraines, la sécurité des systèmes embarqués par rapport à un large panel de modèles d’attaquants, et à l’aide de contre-mesures efficaces énergétiquement et en matière de performances.

Une communauté de 80 chercheurs, enseignants chercheurs et ingénieurs mobilisant :

2 ingénieurs de recherche, 20 doctorants, 7 post-doctorants

Publications

Les autres projets du PEPR Cybersécurtié